Product Summary

The MB90349CAPF-G-154 is a 16-bit Proprietary Microcontroller especially designed for automotive and other industrial applications. Its main feature are the on-board CAN Interfaces, which conform to V2.0 Part A and Part B, while supporting a very flexible message buffer scheme and so offering more functions than a normal full CAN approach. With the new 0.35 µm CMOS technology, the MB90349CAPF-G-154 offers on-chip FLASH-ROM program memory up to 512 Kbytes. The power supply (3 V) is supplied to the internal MCU core from an internal regulator circuit. This creates a major advantage in terms of EMI and power consumption. The internal PLL clock frequency multiplier provides an internal 42 ns instruction cycle time from an external 4 MHz clock. The MB90349CAPF-G-154 unit features an 8 channel Output Compare Unit and 8 channel Input Capture Unit with 2 separate 16-bit free running timers. 4 UARTs constitute additional functionality for communication purposes.

Parametrics

MB90349CAPF-G-154 absolute maximum ratings: (1)Power supply voltage, VCC: VSS - 0.3 to VSS + 6.0 V; AVCC: VSS - 0.3 VSS + 6.0 V; AVRH, AVRL: VSS - 0.3 to VSS + 6.0 V; (2)Input voltage, VI: VSS - 0.3 to VSS + 6.0 V; (3)Output voltage, VO: VSS - 0.3 to VSS + 6.0 V ; (4)Maximum Clamp Current, ICLAMP: -4.0 to +4.0 mA; (5)Total Maximum Clamp Current, Σ|ICLAMP|: 40 mA ; (6)L level maximum output current, IOL: 15 mA; (7)L level average output current, IOLAV: -4mA; (8)L level maximum overall output current, ΣIOL: 100 mA; (9)L level average overall output current, ΣIOLAV: 50 mA ; (10)H level maximum output current, IOH: -15 mA; (11)H level average output current, IOHAV: -4mA; (12)H level maximum overall output current, ΣIOH: -100 mA; (13)H level average overall output current, ΣIOHAV: -50 mA; (14)Power consumption, PD: 340 mW; (15)Operating temperature, TA: -40 to +105℃; (16)Storage temperature, TSTG: -55 to +150℃.

Features

MB90349CAPF-G-154 features: (1)Built-in PLL clock frequency multiplication circuit; (2)Selection of machine clocks (PLL clocks) is allowed among frequency division by two on oscillation clock, and multiplication of 1 to 6 times of oscillation clock (for 4 MHz oscillation clock, 4 MHz to 24 MHz); (3)Operation by sub-clock (up to 50 kHz : 100 kHz oscillation clock divided two) is allowed. (devices without S-suffix only); (4)Minimum execution time of instruction : 42 ns (when operating with 4-MHz oscillation clock, and 6-time multi-plied PLL clock); (5)Built-in Clock Modulation circuit; (6)Wide choice of data types (bit, byte, word, and long word); (7)Wide choice of addressing modes(23 types); (8)Enhanced multiply-divide instructions and RETI instructions; (9)Enhanced high-precision computing with 32-bit accumulator; (10)Employing system stack pointer; (11)Enhanced various pointer indirect instructions; (12)Barrel shift instructions.

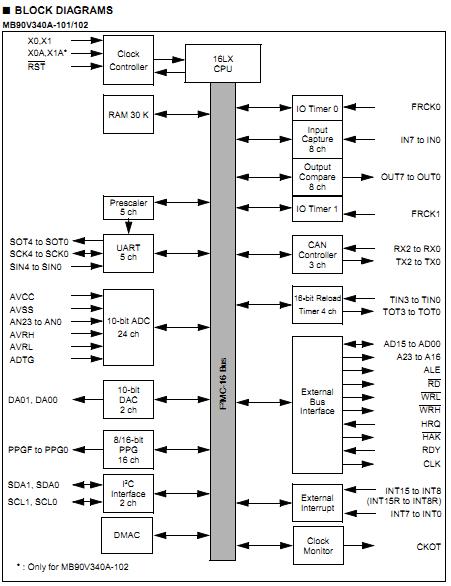

Diagrams

|

MB90050 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MB90091A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MB90092 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MB90096 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MB90097 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

MB90098A |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))